UNITED STATES DEPARTMENT OF COMMERCE United States Patent and Trademark Office Address: COMMISSIONER FOR PATENTS P.O. Box 1450 Alexandria, Virginia 22313-1450 www.uspto.gov

| APPLICATION NO.                                         | FILING DATE                              | FIRST NAMED INVENTOR | ATTORNEY DOCKET NO.   | CONFIRMATION NO. |  |

|---------------------------------------------------------|------------------------------------------|----------------------|-----------------------|------------------|--|

| 12/283,652                                              | 09/15/2008                               | Neville Carvalho     | A02891                | 8429             |  |

|                                                         | 45851 7590 07/08/2016<br>Treyz Law Group |                      |                       | EXAMINER         |  |

| 870 Market Street, Suite 984<br>San Francisco, CA 94102 |                                          |                      | FOTAKIS, ARISTOCRATIS |                  |  |

|                                                         |                                          |                      | ART UNIT              | PAPER NUMBER     |  |

|                                                         |                                          |                      | 2633                  |                  |  |

|                                                         |                                          |                      | NOTIFICATION DATE     | DELIVERY MODE    |  |

|                                                         |                                          |                      | 07/08/2016            | ELECTRONIC       |  |

# Please find below and/or attached an Office communication concerning this application or proceeding.

The time period for reply, if any, is set in the attached communication.

Notice of the Office communication was sent electronically on above-indicated "Notification Date" to the following e-mail address(es):

docket@treyzlawgroup.com

### UNITED STATES PATENT AND TRADEMARK OFFICE

\_\_\_\_

## BEFORE THE PATENT TRIAL AND APPEAL BOARD

Ex parte NEVILLE CARVALHO, ALLAN THOMAS DAVIDSON, ANDY TURUDIC, BRUCE B. PEDERSEN, DAVID W. MENDEL, KALYAN KANKIPATI, MICHAEL MENGHUI ZHENG, SERGEY SHUMARAYEV, SEUNGMYON PARK, TIM TRI HOANG, and KUMARA THARMALINGAM

> Appeal 2015-001076 Application 12/283,652 Technology Center 2600

Before JEAN R. HOMERE, JESSICA C. KAISER, and SHARON FENICK, *Administrative Patent Judges*.

KAISER, Administrative Patent Judge.

### **DECISION ON APPEAL**

Appellants<sup>1</sup> appeal under 35 U.S.C. § 134(a) from the Examiner's final rejection of claims 1, 4–14, 16–18, 24–28, 30–36, and 39.<sup>2</sup> We have jurisdiction under 35 U.S.C. § 6(b).

We reverse.

<sup>&</sup>lt;sup>1</sup> According to Appellants, the real party in interest is Altera Corp. (App. Br. 2.)

<sup>&</sup>lt;sup>2</sup> The Examiner indicated claims 19–23 are allowable. (Final Act. 12.) Claims 2, 3, 15, 29, 37, and 38 have been canceled. (App. Br. 2.) Although the Final Office Action lists claim 29 as pending (Final Act. 1), Appellants canceled that claim in their Amendment dated May 24, 2013.

## **EXEMPLARY CLAIMS**

Claims 1 and 14 are exemplary and are reproduced below:

1. A transceiver system comprising:

a word aligner, wherein each word of a plurality of words aligned by the word aligner has a plurality of bits and the word aligner aligns the plurality of words to a word boundary; and

a bit slipper coupled to the word aligner;

wherein the bit slipper receives information regarding word alignment from the word aligner, further wherein the bit slipper slips bits in such a way so that total delay due to word alignment by the word aligner and bit slipping by the bit slipper is constant for all phases of a recovered clock signal.

# 14. A method comprising:

aligning words to a desired word boundary, wherein each of the words has a plurality of bits;

receiving from a word aligner, by a bit slipper, information regarding the aligning; and

slipping bits of the words, wherein total delay due to the aligning and the slipping is constant for all phases of a recovered clock signal,

wherein the aligning and the slipping are performed by a transceiver system.

### **REJECTIONS**

The Examiner has rejected claims 14 and 16 under 35 U.S.C. § 101 as being directed to non-statutory subject matter. (Final Act. 2–3.)

The Examiner has rejected claims 1, 4, 5, 12–14, 16, and 39 under 35 U.S.C. § 102(e) as being anticipated by Cory (US 7,913,014 B1; issued Mar. 22, 2011). (Final Act. 3–5.)

The Examiner has rejected claims 10 and 11 under 35 U.S.C. § 103(a) as being unpatentable over Cory and Appellants' Admitted Prior Art ("AAPA"). (Final Act. 6.)

The Examiner has rejected claims 6–9, 17, 18, 24–28, and 33–35 under 35 U.S.C. § 103(a) as being unpatentable over Cory and Moyal (US 6,744,323 B1; issued June 1, 2004). (Final Act. 7–12.)

## **ANALYSIS**

# Statutory Subject Matter

The Examiner rejected claims 14 and 16 under 35 U.S.C. § 101 because the Examiner found those claims were directed to an ineligible abstract idea. (Final Act. 3.) The Examiner finds that claim 14 is "a mere statement of a general concept," and that its recitation of a "transceiver system," a "recovered clock signal," and the functions of aligning and slipping are insufficient to make the claim patent eligible. (*Id.* at 13; Adv. Act. 3; *see also* Ans. 2–6.) Specifically, the Examiner finds claim 14 is directed to the abstract idea of "bit slipping according to information regarding the aligning of words." (Ans. 3.) Appellants argue the Examiner erred in finding claims 14 and 16 are directed to an abstract idea. (App. Br. 6–9; Reply Br. 1–3.)

A patent may be obtained for "any new and useful process, machine, manufacture, or composition of matter, or any new and useful improvement thereof." 35 U.S.C. § 101. The Supreme Court has held that "this provision contains an important implicit exception: Laws of nature, natural phenomena, and abstract ideas are not patentable." *Alice Corp. Pty. Ltd. v.*

CLS Bank Int'l, 134 S. Ct. 2347, 2354 (2014) (internal citation and quotation omitted).

In *Alice*, the Supreme Court reaffirmed the framework set forth previously in *Mayo Collaborative Services v. Prometheus Laboratories, Inc.*, 132 S. Ct. 1289 (2012), "for distinguishing patents that claim laws of nature, natural phenomena, and abstract ideas from those that claim patent-eligible applications of these concepts." *Alice*, 134 S. Ct. at 2355. The first step in the analysis is to "determine whether the claims at issue are directed to one of those patent-ineligible concepts." *Id.* If so, the second step is to consider the elements of the claims "individually and 'as an ordered combination' to determine whether the additional elements 'transform the nature of the claim' into a patent-eligible application." *Id.* (quoting *Mayo*, 132 S. Ct. at 1298, 1297). In other words, the second step is to "search for an 'inventive concept' — i.e., an element or combination of elements that is 'sufficient to ensure that the patent in practice amounts to significantly more than a patent upon the [ineligible concept] itself." *Id.* (brackets in original) (quoting *Mayo*, 132 S. Ct. at 1294).

Recently in *Enfish*, *LLC v. Microsoft Corp.*, \_ F.3d \_, No. 2015-1244, 2016 WL 2756255, at \*4 (Fed. Cir. May 12, 2016), the Federal Circuit explained that "directed to" under step one of the *Alice* framework, "applies a stage-one filter to claims, considered in light of the specification, based on whether 'their character as a whole is directed to excluded subject matter.'" (internal citation omitted). The Federal Circuit further explained that improvements in computer-related technology, including software improvements, are not inherently abstract, and thus, it is "relevant to ask whether the claims are directed to an improvement to computer functionality

versus being directed to an abstract idea, even at the first step of the *Alice* analysis." *Id.* Specifically, the Federal Circuit differentiated between claims that focus on an improvement in computer capabilities and claims that focus on an abstract idea "for which computers are invoked merely as a tool." *Id.* at \*5. In *Enfish*, the Federal Circuit determined that the claimed self-referential database table was directed to an improvement in the functioning of a computer and not "a situation where general-purpose computer components are added post-hoc to a fundamental economic practice or mathematical equation." *Id.* at \*7–8. Thus, the court determined that the claims at issue were not directed to an abstract idea and therefore the claims were patent eligible under 35 U.S.C. § 101. *Id.*

Here, the methods of claims 14 and 16 relate to latency uncertainty reduction in a transceiver system (i.e., a constant total delay due to word aligning and bit slipping in claim 14 and a total delay of zero in claim 16). The Specification explains that receiver 110 includes deserializer 113 to convert incoming serial data to parallel data. (Spec. ¶ 5, Fig. 1 (identified as Prior Art).) Such a system can also use a divider 116 to produce a recovered clock with N phases, and the deserializer also produces N different word orderings. (Spec. ¶ 6, Fig. 2 (identified as Prior Art).) Word aligner 120 receives the parallel words and aligns them to a desired word boundary. (Spec. ¶ 7, Fig. 1.) The Specification teaches, however, that doing so introduces "a Deserializer/Word aligner latency uncertainty." (Spec. ¶ 7.) In one embodiment, the Specification solves this problem of latency uncertainty by using a bit slipper so that the total delay from word aligning and bit slipping is constant for all recovered clock phases, which "allows for

having a fixed and known latency between the receipt and transmission of bits for all phases of parallelization by the deserializer." (Spec.  $\P$  16.)

Because *Enfish* issued after this appeal was docketed, the Examiner did not have the opportunity to evaluate claims 14 and 16 under the principles set forth in that case or the Memorandum to the Patent Examining Corps, dated May 19, 2016 and titled "Recent Subject Matter Eligibility Decisions (*Enfish, LLC v. Microsoft Corp.* and *TLI Communications LLC v. A.V. Automotive, LLC*)" (available at http://www.uspto.gov/sites/default/files/documents/ieg-may-2016\_enfish\_memo.pdf). Nevertheless, we determine that claims 14 and 16, like the claims in *Enfish*, are directed to an improvement in the functioning of a computer (i.e., eliminating word aligner latency delay uncertainty) and not to the addition of general-purpose computer components to a fundamental economic practice or mathematical equation. Accordingly, we conclude that claims 14 and 16 are not directed to an abstract idea under the first step of the *Alice* analysis, and we do not sustain the Examiner's § 101 rejection of claims 14 and 16.

# Anticipation

Appellants argue the Examiner erred in finding Cory discloses "the bit slipper slips bits in such a way so that <u>total delay due to word alignment by the word aligner and bit slipping by the bit slipper is constant for all phases of a recovered clock signal,"</u> as recited in claim 1. (App. Br. 9–11.) Specifically, Appellants contend Cory discloses its total delay is variable (*id.* at 9) and that the Examiner misconstrued "total delay" as "the overall final latency after bit slipping" instead of "total delay due to word alignment by the word aligner and bit slipping by the bit slipper" as claimed (*id.* at 9–10).

Appellants further contend Cory's disclosure that "slip control block 302 issues a toggle signal to data alignment block 216, which toggles the data alignment of data bytes received from deserializer 208 between one of two possible settings, i.e., 0 UI or 1 UI," refers to the delay introduced by data alignment block 216 and not to the recited "total delay." *Id.* at 10 (quoting Cory 7:66–8:2); *see also id.* (arguing the disclosure at Cory 11:65–67, 12:1–2, 34–40 does not disclose a constant total delay of 0 UI (unit intervals) but rather a latency of 0 or 1 UI); *id.* at 10–11 (arguing that the disclosure at Cory 12:29 shows the "latency" in Cory is not the recited "total delay" but rather the latency generated by data alignment step 806).

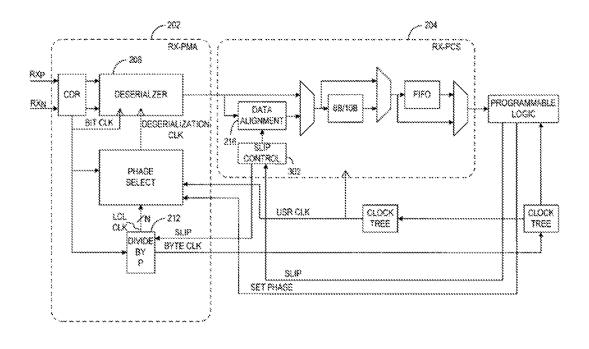

Figure 3 of Cory is reproduced below:

Figure 3 of Cory, reproduced above, depicts a transceiver that implements a phase rotation granularity of 1 UI. (Cory 7:56–61.) The

FIG. 3

Examiner finds that deserializer 208³ discloses the recited "word aligner" and data alignment 216 discloses the recited "bit slipper." (Ans. 7.) The Examiner also clarifies that "total delay" was interpreted as "the overall final latency caused by the word aligning and bit slipping." (*Id.*) The Examiner further finds the delay introduced by data alignment block 216 is "the delay needed to correct the delay introduced by the deserializer 208 (word aligner) to a total delay of 0UI or 1UI." (*Id.* at 8.) The Examiner further finds "Cory teaches that the latency is 0UI or 1UI according to the selected clock (deserialization clock, Fig. 3), where each clock signal by definition has a plurality of phases." (*Id.*; *see also* Final Act. 3–4 (citing Cory 7:9–14, 8:1–2, 32–35); Adv. Act. 5 (citing Cory 11:65–12:2, 12:34–40).)

Appellants argue the Examiner's interpretation of Cory is erroneous because it is not supported by evidence and is inconsistent with Cory's disclosure. (Reply Br. 3–4.) In particular, Appellants argue Cory's disclosure that "data alignment block 216... toggles the data alignment of data bytes received from deserializer 208 between one of two possible settings, i.e., 0 UI or 1 UI" means that the data alignment by data alignment block 216 is 0 UI or 1 UI, not that the "total delay" is 0 or 1 UI. (*Id.* at 4 (citing Cory 7:67–8:2).)

We are persuaded by Appellants' arguments. The portions of Cory relied upon by the Examiner do not disclose that "total delay due to word alignment by the word aligner and bit slipping by the bit slipper is constant for all phases of a recovered clock signal." In particular, we agree with

<sup>&</sup>lt;sup>3</sup> We understand the Examiner's reference to item 218 (Ans. 7) to be a typographical error. (*See* Ans. 8 (referring to deserializer 208 as the recited "word aligner"); Final Act. 3 (same); Adv. Act. 5 (same).)

Appellants (App. Br. 10; Reply Br. 3) that "slip control block **302** issues a toggle signal to data alignment block **216**, which toggles the data alignment of data bytes received from deserializer **208** between one of two possible settings, i.e., 0 UI or 1 UI" (Cory 7:66–8:2) refers to the delay introduced by data alignment block 216 (i.e., 0 or 1 UI) and not to the recited "total delay."

In addition, the Examiner cites portions of Cory that discuss checking the latency after data alignment block 216 and reducing the latency if its magnitude is an unacceptable level. (Adv. Act. 5 (citing Cory 11:65–12:2, 12:34–40).) However, the Examiner has not adequately shown how a procedure that reduces latency to an acceptable level discloses that the latency is constant for all phases of a recovered clock signal, as recited in claim 1. Thus, we find the Examiner has not adequately shown that Cory discloses "total delay due to word alignment by the word aligner and bit slipping by the bit slipper is constant for all phases of a recovered clock signal."

For the reasons discussed above, we do not sustain the Examiner's § 102(e) rejection of claim 1, independent claim 14 which recites a substantially similar limitation (App. Br. 12; Final Act. 3), and dependent claims 4, 5, 12, 13, 16, and 39.

### **Obviousness**

The Examiner has rejected claims 10 and 11 under 35 U.S.C. § 103(a) as being unpatentable over Cory and AAPA. (Final Act. 6.) Claims 10 and 11 depend directly or indirectly from claim 1, and AAPA as applied by the Examiner (*id.*) does not cure the deficiency in the Examiner's rejection of

claim 1 as discussed above. Accordingly, we do not sustain the Examiner's § 103 rejection of claims 10 and 11.

In addition, the Examiner has rejected claims 6–9, 17, 18, 24–28, and 33–35 under 35 U.S.C. § 103(a) as being unpatentable over Cory and Moyal. (Final Act. 7–12.) Claims 6–9 depend directly or indirectly from claim 1, and claims 17 and 18 depend from claim 14. The additional reference (Moyal) as applied by the Examiner (Final Act. 7–9) in the § 103(a) rejection of those claims does not cure the deficiency in the Examiner's rejection of claims 1 and 14. Accordingly, we do not sustain the Examiner's § 103(a) rejection of claims 6–9, 17, and 18.

Independent claims 24 and 33 recite limitations similar to the limitation of claim 1 discussed above, and in rejecting independent claims 24 and 33, the Examiner relied on the same disclosure in Cory as teaching those limitations (Final Act. 9). Accordingly, for the reasons discussed above for claim 1, we do not sustain the Examiner's § 103(a) rejection of independent claims 24 and 33, and dependent claims 25–28, 34, and 35.

### **DECISION**

We reverse the Examiner's decision to reject claims 14 and 16 under 35 U.S.C. § 101.

Appeal 2015-001076 Application 12/283,652

We reverse the Examiner's decision to reject claims 1, 4, 5, 12–14, 16, and 39 under 35 U.S.C. § 102(e).

We reverse the Examiner's decision to reject claims 6–11, 17, 18, 24–28, and 33–35 under 35 U.S.C. § 103(a).

# **REVERSED**